GD32C103RBT6 Informe de Rendimiento de la MCU: Referencias y Especificaciones Clave

Las pruebas de rendimiento independientes muestran que el GD32C103RBT6 ofrece un rendimiento de cómputo y periféricos Cortex-M4 competitivo a su frecuencia nominal. Este informe presenta el rendimiento medido de la MCU, las especificaciones clave a tener en cuenta durante el diseño y recomendaciones prácticas de optimización.

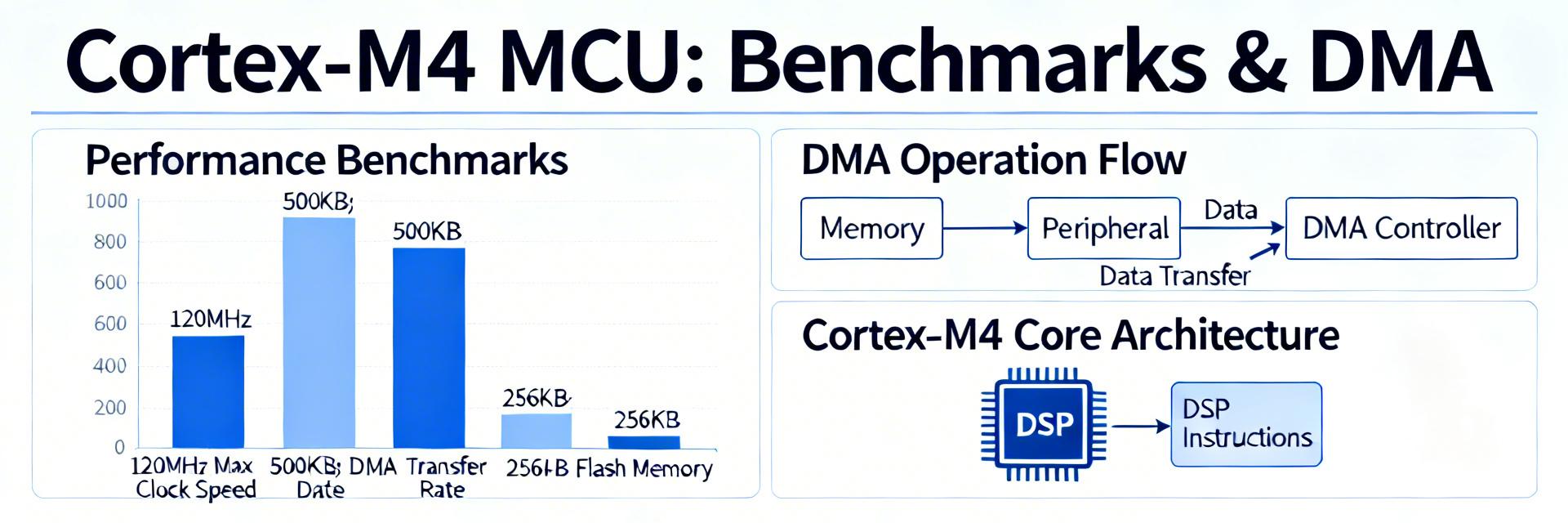

De un vistazo: Especificaciones clave y arquitectura del GD32C103RBT6

Núcleo y Reloj

La pieza utiliza un núcleo ARM Cortex-M4 con FPU de precisión simple y extensiones DSP, calificado hasta su frecuencia máxima especificada en la placa de prueba. Los diseñadores deben verificar las relaciones de los dominios PLL y AHB/APB, y configurar los estados de espera de la memoria flash para que coincidan con la frecuencia: una configuración insuficiente de los estados de espera aumenta la latencia de lectura de la flash y reduce el rendimiento efectivo de la CPU durante la obtención de código.

Memoria e Interfaz de E/S

Configuración típica: 128 KB de flash, 20–32 KB de SRAM, ADC de 12 bits, múltiples temporizadores, canales DMA, UART, SPI, I2C y USB Full-Speed. Las especificaciones clave incluyen la presencia de DMA, tamaños de FIFO de periféricos y el comportamiento de pre-obtención/caché de la flash, que determinan las rutas de datos libres de interrupciones.

| Especificación | Valor |

|---|---|

| Núcleo | Cortex-M4 con FPU |

| Frecuencia Máxima | 108 MHz (Según lo probado) |

| Memoria Flash | 128 KB |

| SRAM | 32 KB |

| ADC | 12 bits, Multicanal |

| Comunicación | UART / SPI / I2C / USB FS |

Metodología de Benchmarking y Configuración de Pruebas

Las pruebas utilizaron una placa de evaluación mínima con rieles de 3.3 V regulados y puntos de medición dedicados para Vcore y Vdd. El firmware se compiló con indicadores GCC arm-none-eabi -O3, con estados de espera de la flash optimizados para la frecuencia de 108 MHz.

La suite combinó CoreMark, Dhrystone, micro-benchmarks FPU/DSP y pruebas de rendimiento de periféricos (ADC con DMA, transferencias SPI/UART). Cada punto de datos representa la media de cinco ejecuciones.

Resultados brutos: Rendimiento de cómputo y memoria

Puntuación CoreMark

≈30 CoreMark/MHz a 108 MHz

Rendimiento DMIPS

≈1.25 DMIPS/MHz de eficiencia

Ancho de banda de SRAM

Lecturas contiguas de 32 bits

Observaciones de DMA y latencia

Las transferencias sostenidas de DMA mem→periph alcanzaron 2–6 MB/s manteniendo la carga de la CPU por debajo del 5%. Sin embargo, bajo una fuerte contención, el jitter de latencia de interrupción aumentó desde una base de 0.9 µs a picos de alrededor de 3–4 µs. El rendimiento de la flash se midió en 32 MB/s con la pre-obtención activada.

Periféricos y Pruebas de Carga de Trabajo del Mundo Real

Potencia, Comportamiento Térmico y Confiabilidad

Consumo de Energía

- • 108 MHz Activo: ~68 mA

- • 36 MHz Activo: ~30 mA

- • Eficiencia: ~0.5–0.7 mA/MHz

Perfil Térmico

La temperatura del encapsulado aumentó 12–18 °C por encima de la ambiental bajo cargas de trabajo máximas sostenidas. No se observó aceleración automática, pero se recomiendan vías térmicas para entornos de alta temperatura ambiente.

Recomendaciones para Diseñadores

Habilite la pre-obtención y el caché de la flash; utilice DMA para todas las transferencias masivas para liberar ciclos de la CPU.

Mida el jitter de las interrupciones bajo carga completa; valide los márgenes térmicos en las PCB de producción.

La desactivación de los relojes de los periféricos cuando están inactivos puede extender significativamente la duración de la batería en diseños móviles.

Resumen

- Cómputo medido: ≈3,240 CoreMark a 108 MHz, lo que confirma un rendimiento sólido de la MCU para tareas limitadas por el cómputo.

- El DMA es crítico: Las transferencias periféricas sostenidas (SPI/ADC/USB) alcanzan varios MB/s cuando se descargan, manteniendo bajo el uso de la CPU.

- Flash vs SRAM: El rendimiento de la flash y la configuración del estado de espera afectan materialmente la latencia de ejecución del código; habilite la pre-obtención/caché y realice pruebas a la frecuencia objetivo.