Hoja de datos de GDP2BFLM-WB Buceo profundo: Especificaciones y tiempos completos

Este análisis profundo destaca las cifras principales de la hoja de datos del GDP2BFLM-WB: velocidad máxima de datos de hasta 1866 Mbps, CAS típico 13–13–13 y densidad de 4 Gbit (256 Mb x16). Estas cifras determinan el ancho de banda, el margen de temporización y los compromisos térmicos/de potencia para los diseñadores de sistemas.

Un recorrido práctico basado en especificaciones para que los ingenieros validen rápidamente las opciones eléctricas, de temporización, de PCB y de verificación.

La visibilidad temprana sobre la velocidad máxima, el CAS y la densidad reduce los candidatos de diseño. Enumera el funcionamiento a 1866 Mbps con CAS 13–13–13.

Antecedentes y descripción general del paquete

Atributos clave del dispositivo de un vistazo

La organización del dispositivo es de 4 Gbit (256 Mb x16), señalización de clase DDR3/DDR3L con comportamiento de alimentación DDR3L. Este conjunto de especificaciones de una sola línea permite a los arquitectos decidir el ajuste de capacidad y ancho de banda antes de realizar comprobaciones eléctricas más profundas.

Paquete, distribución de pines y entorno ambiental

La pieza utiliza un paquete de estilo FBGA con llamadas de huella recomendadas típicas y un rango operativo hasta el límite industrial de alta gama (ejemplo: –40 °C a 95 °C). Se requieren comprobaciones de la huella a nivel de placa y reducción de potencia térmica para un funcionamiento continuo a 1866 Mbps.

Especificaciones eléctricas y mecánicas completas

| Parámetro | Detalles de la especificación | Enfoque de ingeniería |

|---|---|---|

| Eléctrico (VDD/VDDQ) | Clase DDR3L (≈1,35 V nominal) | Verificar la tolerancia y el comportamiento de VTT |

| Estilo de paquete | FBGA con mapa de bolas/almohadillas | Coincidencia del patrón de tierra de la PCB |

| Fiabilidad | Guía MSL y resistencia térmica | Manejo de la humedad y presupuesto de PDN |

Análisis profundo de las especificaciones de temporización

Temporizaciones de lectura/escritura y parámetros clave

Los parámetros principales incluyen tCK, tCL (CAS), tRCD, tRP, tRAS, tWR y tRFC. Los diseñadores deben calcular la latencia en el peor de los casos sumando las latencias de comando (tRCD + tCL + ciclos CAS) y verificar la estabilidad del período de reloj.

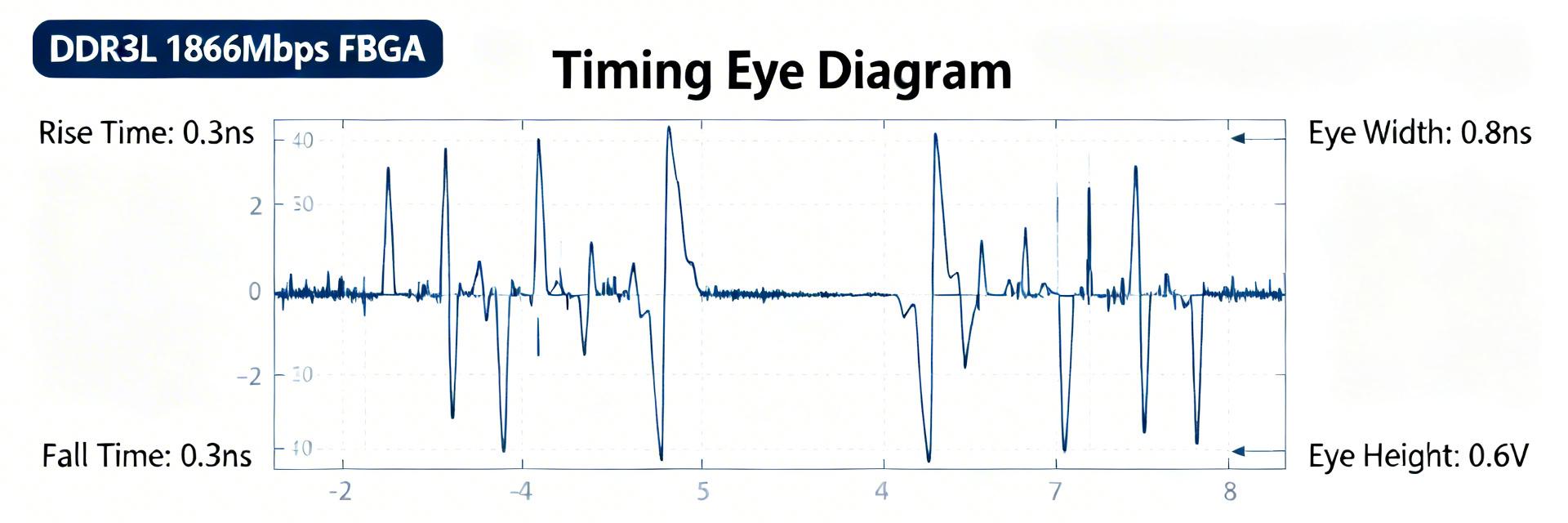

Diagramas de temporización, comprobaciones de margen y de configuración/mantenimiento

Los diagramas de forma de onda en la hoja de datos definen las restricciones de configuración/mantenimiento (por ejemplo, margen de configuración ≥0,15 UI). Utilice estos como criterios de aprobación/falla en la simulación y validación de laboratorio para garantizar una captura de datos robusta.

Directrices de PCB e integridad de señal

Enrutamiento e impedancia

- ▸ Emparejar pares DQS/DQ (desviación de unas pocas decenas de milésimas de pulgada)

- ▸ Trazas controladas de 50 Ω/100 Ω

- ▸ Evitar derivaciones (stubs) en las redes de comando/dirección

PDN y reloj

- ▸ Condensadores de desacoplamiento cerca de los pines del dispositivo

- ▸ Apilamiento de planos de baja impedancia

- ▸ Rutas de retorno de VDD cortas para minimizar el jitter

Estudio de caso de integración: Implementación de 1866 Mbps

Integración de referencia: Siga una puesta en marcha por etapas. Comience con un reloj conservador, ejecute el entrenamiento de memoria y el estrés de lectura/escritura, luego aumente incrementalmente la velocidad de datos mientras monitorea los diagramas de ojo y el IDD.

Errores comunes: Fallos en el margen de temporización, errores inducidos por la integridad de señal (SI) y estrangulamiento térmico. Remedie agregando margen, reduciendo el recuento de vías o mejorando el desacoplamiento.

Lista de verificación accionable

Resumen clave

- Haga coincidir tempranamente la capacidad del dispositivo y la velocidad máxima de 1866 Mbps con el ancho de banda del sistema; priorice el margen de temporización y el margen de maniobra de la PDN.

- Valide los límites eléctricos: confirme las tolerancias de VDD/VDDQ y el IDD bajo extremos de carga.

- Siga una puesta en marcha por etapas: primero entrenamiento a baja velocidad, luego aumentos incrementales de la velocidad con comprobaciones de SI.