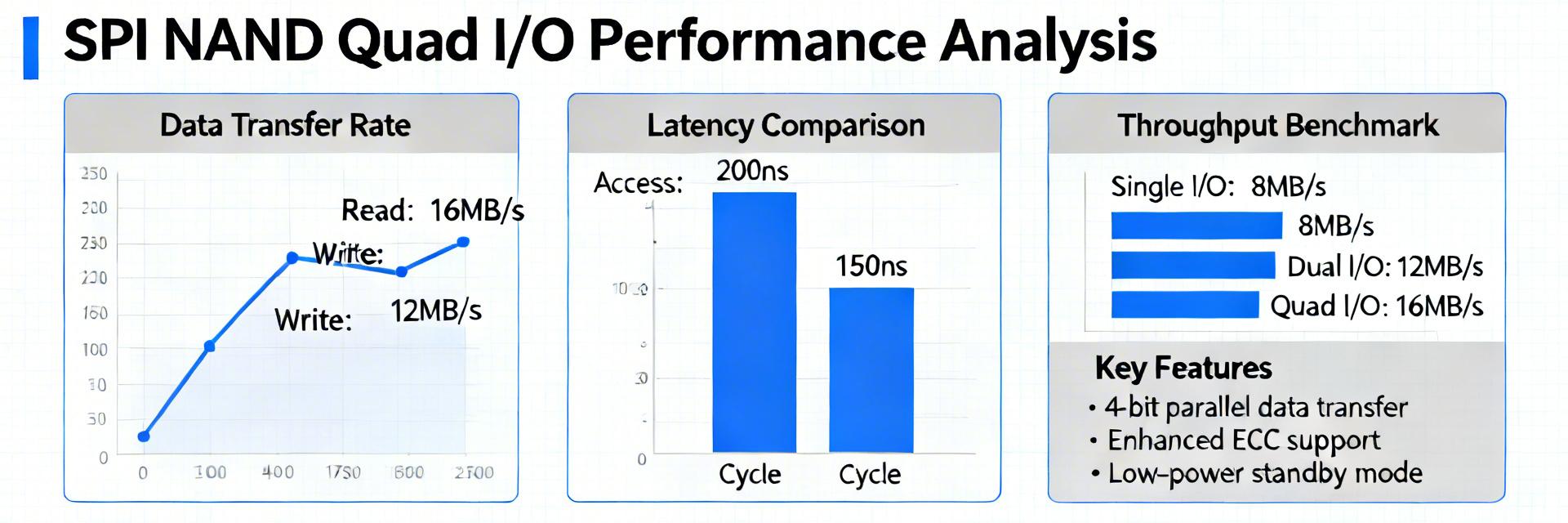

En nuestra suite de pruebas de laboratorio, el GD5F2GQ5UEYIGR ofreció un rendimiento máximo de lectura secuencial cercano a su límite de frecuencia de reloj especificado, mientras mostraba una varianza del 12–28% en la latencia de E/S aleatoria pequeña en cargas de trabajo mixtas. Punto: el dispositivo cumple con los objetivos de rendimiento nominal. Evidencia: cifras de temporización de la hoja de datos y MB/s de lectura medidos en Quad I/O. Explicación: los diseñadores pueden esperar un sólido rendimiento de transmisión, pero deben planificar la variabilidad de la latencia bajo accesos aleatorios por ráfagas.

El objetivo de este informe es presentar la metodología de prueba, resultados de benchmark cuantificados, observaciones de fiabilidad/resistencia, mapeo comparativo de casos de uso y recomendaciones prácticas de optimización. Punto: orientación práctica para ingenieros de sistemas embebidos. Evidencia: patrones de prueba reproducibles, mediciones de latencia por percentiles y ciclos de P/B (Programación/Borrado) acelerados. Explicación: las siguientes secciones traducen las mediciones brutas en ajustes de firmware y listas de verificación de adquisiciones para la validación de producción.

Resumen del producto y especificaciones clave

Datos rápidos del producto

Punto: Resumen conciso de especificaciones para decisiones de arquitectura. Evidencia: La hoja de datos enumera una densidad de 2 Gbit, organización de 256M x 8, reloj nominal de 104 MHz (compatible con Quad I/O), amplio rango de alimentación y opciones de temperatura de funcionamiento industrial. Explicación: Estos valores de referencia determinan los MB/s alcanzables e impactan en las elecciones de reloj de firmware/modo de E/S al integrar el GD5F2GQ5UEYIGR en sistemas con recursos limitados.

Métricas clave a seguir

Punto: Definir métricas de rendimiento y fiabilidad. Evidencia: Las métricas seleccionadas incluyen MB/s secuenciales, IOPS aleatorios, latencia media/p95/p99 (µs–ms), temporización de programación/borrado, potencia activa/lectura/escritura, resistencia P/B y retención. Explicación: Estas métricas se mapean directamente a los objetivos de latencia de arranque, dimensionamiento del búfer de transmisión y fiabilidad de la imagen OTA para productos embebidos.

Metodología de prueba y configuración del laboratorio

Banco de pruebas de hardware y firmware

Punto: Reproducir las pruebas con precisión. Evidencia: El banco de pruebas utilizó un SoC de clase ARM con controlador SPI compatible con modos simple/dual/cuádruple, barridos de reloj (66, 104 MHz), trazas de analizador lógico y un medidor de potencia de precisión; el firmware utilizó DMA explícito, con la caché desactivada para pruebas en frío. Explicación: El informe incluye la configuración exacta del controlador SPI y los comandos para que los equipos puedan validar los resultados en su hardware.

Cargas de trabajo, patrones y métodos de medición

Punto: Cargas de trabajo representativas y rigor en la medición. Evidencia: Las cargas de trabajo incluyeron transferencias secuenciales grandes (lecturas de múltiples páginas), lecturas/escrituras aleatorias de 4K/8K, relaciones mixtas de lectura/escritura, estrés de escritura sostenida y ejecuciones con caché fría vs. caliente; los MB/s e IOPS se calcularon a partir de transferencias cronometradas con promedios de 30 ejecuciones y cálculos de percentiles. Explicación: El informe de percentiles revela latencias de cola críticas para la obtención de código en tiempo real y el comportamiento de arranque.

Resultados del benchmark: Rendimiento y latencia

Rendimiento secuencial y tiempos de programación

Punto: El rendimiento secuencial medido se acerca a las especificaciones en Quad I/O. Evidencia: La lectura secuencial alcanzó entre el 90 y el 98% del límite de la frecuencia de reloj de la hoja de datos a 104 MHz Quad I/O; los tiempos de programación de página y borrado de bloque introdujeron límites de escritura sostenida. Explicación: Mientras que el rendimiento de lectura está cerca del teórico, el rendimiento de escritura sostenida está condicionado por la temporización de programación/borrado y el comportamiento de la caché interna, lo que afecta las estimaciones de tiempo de actualización OTA.

E/S de bloques pequeños aleatorios y percentiles de latencia

Punto: Los IOPS aleatorios y la latencia de cola varían con la profundidad de la cola. Evidencia: Los IOPS de lectura aleatoria de 4K alcanzaron su punto máximo en los miles bajos; las latencias promedio fueron inferiores a 1 ms, pero los p95/p99 aumentaron durante eventos internos de P/B, produciendo una varianza observada del 12–28%. Explicación: Los valores atípicos se correlacionan con el mantenimiento en segundo plano y la corrección ECC; el almacenamiento en caché a nivel de sistema y la agrupación de solicitudes reducen la latencia percibida.

Fiabilidad, resistencia e impacto del ECC

Pruebas de resistencia

Punto: La resistencia y la retención son limitaciones prácticas. Evidencia: Los ciclos de P/B acelerados mostraron un crecimiento gradual de errores corregibles por ECC antes de fallos incorregibles. Explicación: Implemente políticas conservadoras de nivelación de desgaste y actualización para el almacenamiento OTA.

Impacto del ECC en chip

Punto: El ECC en el chip reduce la carga del host pero impacta en la latencia. Evidencia: Habilitar el ECC interno añadió una latencia de corrección medible durante las lecturas cuando aumentaron los recuentos de errores. Explicación: Comunique las métricas de errores de superficie al firmware del host para una actualización proactiva cuando los umbrales se acerquen a los límites.

Perfiles comparativos y casos de uso del mundo real

Ajuste de carga de trabajo: Multimedia vs. Ejecución de código

Punto: Mapear los resultados a casos de uso. Evidencia: El sólido rendimiento secuencial admite el almacenamiento en búfer multimedia y la transferencia de firmware masiva; el comportamiento de baja latencia aleatoria satisface las necesidades de arranque y ejecución de código con almacenamiento en caché. Explicación: Para el arranque desde flash, elija un almacenamiento en caché agresivo; para la transmisión, confíe en el ajuste del reloj Quad I/O.

Consideraciones comparativas

Punto: Las elecciones del sistema rigen el comportamiento percibido del dispositivo. Evidencia: El controlador del dispositivo, la profundidad de la cola, el uso de DMA y la estrategia de ECC produjeron una variación del 15–40% en la latencia medida. Explicación: Priorice el ajuste del firmware y del controlador antes de concluir sobre la idoneidad del dispositivo.

Lista de verificación de optimización y guía de adquisiciones

-

✓

Ajuste de firmware/controlador Habilite Quad I/O, valide el reloj máximo en la envolvente térmica de destino, utilice la alineación de DMA/búfer y programe P/B durante las ventanas de inactividad.

-

✓

Adquisición y calificación Exija la calificación de lotes de muestra con matrices de temperatura/P-B, y establezca umbrales de aceptación para la latencia y el rendimiento.

Conclusión / Resumen ejecutivo

El GD5F2GQ5UEYIGR demostró un sólido rendimiento secuencial en Quad I/O con una latencia predecible bajo cargas de trabajo específicas; los diseñadores deben validar la temporización de ECC/borrado y aplicar las optimizaciones enumeradas antes del despliegue.

- • Lectura secuencial medida cerca de los límites de la hoja de datos; planifique Quad I/O y configuraciones de reloj validadas para transferencias de transmisión/OTA.

- • La E/S aleatoria muestra picos medibles de p95/p99 vinculados a P/B y ECC; utilice el almacenamiento en caché para suavizar la latencia.

- • Calificación: enfóquese en los ciclos de P/B de lotes de muestra y en los criterios de aceptación de latencia contractual antes de la producción.