GD32E103TBU6 Hoja de datos de inmersión profunda y perspectivas de diseño QFN-36

Dado que los MCU compactos de clase Cortex-M4 alimentan la electrónica industrial y de consumo moderna, las elecciones precisas de diseño determinan el éxito del hardware en el primer intento.

Información clave: La interpretación específica de la hoja de datos y las elecciones precisas del patrón de tierra QFN-36 son críticas. Esta guía proporciona un recorrido centrado en los datos, destacando las tablas y las acciones de diseño verificables que los ingenieros de hardware, diseñadores de PCB y líderes de firmware pueden aplicar de inmediato.

Antecedentes y descripción general del encapsulado

Posición de la familia de dispositivos y especificaciones clave

Comience con el resumen del dispositivo y la tabla de características para mapear rápidamente las limitaciones del sistema. La hoja de datos del GD32E103TBU6 enumera el núcleo de la CPU, el reloj máximo, los tamaños de Flash y RAM, que son esenciales para determinar las opciones del regulador y los presupuestos de memoria.

Huella mecánica QFN-36 y resumen de la distribución de pines (Pinout)

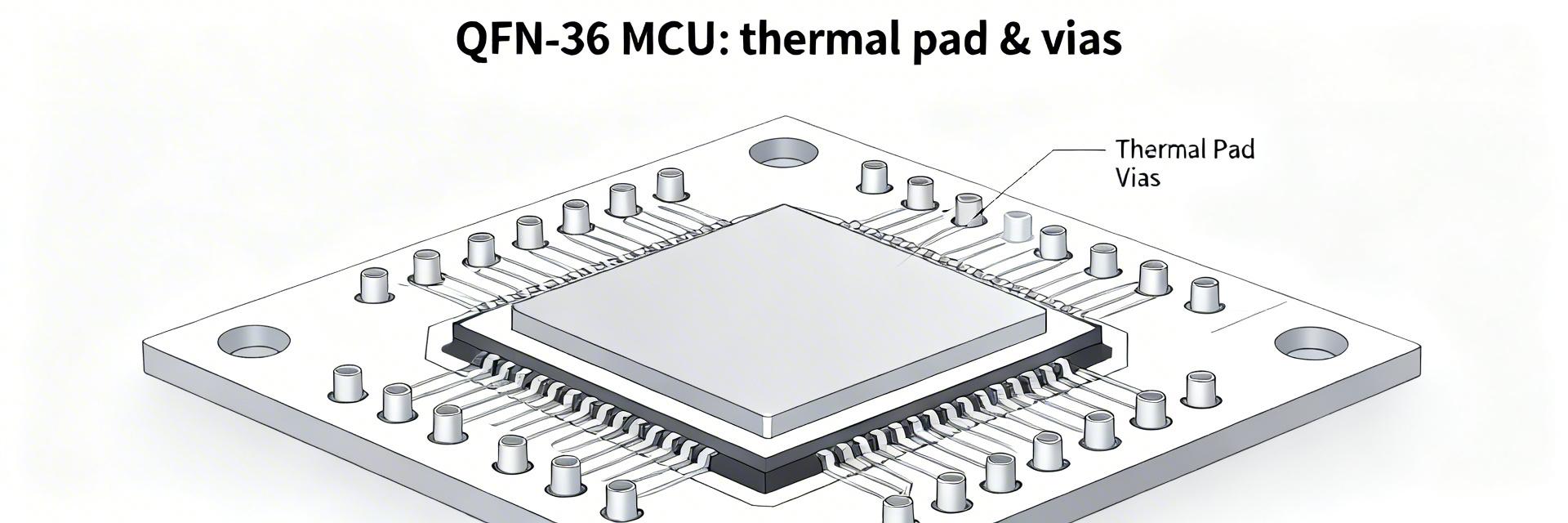

Extraiga el dibujo mecánico para definir su patrón de tierra y el pinout del QFN-36. Las dimensiones clave incluyen el contorno del encapsulado, el número de pads, el tamaño del pad expuesto y la orientación de los pines. La numeración de los pines en la tabla de la hoja de datos identifica los pines críticos de arranque (boot), reinicio (reset) y SWD.

Inmersión profunda en la hoja de datos: Datos eléctricos y térmicos

Máximos absolutos y condiciones de funcionamiento

Distinga entre los máximos absolutos y las condiciones recomendadas para evitar el sobreesfuerzo de los componentes. A continuación, se muestra una vista normalizada de los parámetros operativos:

| Parámetro | Valor mín. | Valor máx. | Unidad |

|---|---|---|---|

| Voltaje de alimentación (VDD) | 2.6 | 3.6 | V |

| Voltaje de entrada de E/S | -0.3 | VDD + 0.3 | V |

| Temperatura de funcionamiento | -40 | 85 / 105 | °C |

Resistencia térmica y visualización de potencia

Convierta la guía θJA/θJC en presupuestos de potencia prácticos para la PCB. Estime la temperatura de la unión con Tj = Ta + P · θJA.

Funciones de los pines y mapeo de periféricos

Estrategia de multiplexación de pines

- ::marker Reserve primero los pines de alimentación, reinicio y arranque.

- ::marker Priorice las interfaces de alta velocidad (SPI/I2C/USART).

- ::marker Bloquee los pines SWD durante la revisión del diseño.

Requisitos de desacoplamiento

Coloque capacitores cerámicos de 0.1µF en cada pin VDD. Use un capacitor de almacenamiento de 4.7–10µF cerca del regulador. Trace las pistas lo más cortas posible para minimizar la inductancia del bucle y la EMI.

Información sobre el diseño de la PCB QFN-36

Diseño del pad térmico y la máscara de soldadura

Traduzca las tolerancias mecánicas en un patrón de tierra conservador. Cree un único pad expuesto con aperturas de pasta de soldadura segmentadas (cobertura del 30–40%) para controlar el volumen de soldadura y evitar huecos o la "flotación" del componente.

Lista de verificación de implementación:

Validación y resolución de problemas

Errores comunes

- Ausencia de vías térmicas en el pad expuesto.

- Capacitancia de desacoplamiento inadecuada.

- Enrutamiento de redes de alta velocidad debajo del núcleo del MCU.

Lista de verificación de puesta en marcha

- Verifique el voltaje y el rizado de VDD/VREF.

- Compruebe la estabilidad del reinicio y del reloj.

- Confirme la conectividad SWD y la temperatura del chip.

Resumen

Comience con el resumen del dispositivo y las tablas de potencia/térmicas. Aplique un diseño conservador de patrón de tierra y vías térmicas para los ensamblajes QFN-36. Las principales acciones de diseño son el diseño correcto del pad expuesto, una rejilla de vías térmicas adecuada y la colocación precisa del desacoplamiento.