GD32E508RET6 Guía completa de especificaciones y benchmarks del mundo real

Perspectiva: Los microcontroladores modernos de clase Cortex-M33 han cambiado fundamentalmente los perfiles de rendimiento integrados. Las comparaciones de laboratorio demuestran un aumento sostenido del rendimiento de DSP del 30–70% a velocidades de reloj más altas. Esta guía evalúa estos avances específicamente para el GD32E508RET6, proporcionando a los ingenieros datos prácticos para una selección de hardware optimizada.

Antecedentes y Descripción General de la Arquitectura

Características del Núcleo y la CPU

El silicio utiliza un núcleo Cortex-M33 con el conjunto de instrucciones ARMv8-M. Las características clave incluyen TrustZone opcional, una Unidad de Protección de Memoria (MPU) y una canalización multietapa de alta eficiencia. Estos elementos mejoran significativamente el rendimiento de un solo hilo, el determinismo de las interrupciones y la partición de seguridad.

Arquitectura de Memoria

La jerarquía de Flash y RAM dicta el rendimiento sostenido. Los estados de espera de la memoria Flash en el chip y la ubicación de la RAM afectan la latencia de obtención (fetch). Los ingenieros deben equilibrar el número de pines del encapsulado frente a las interfaces de memoria externa y los posibles cuellos de botella, como el uso de la Memoria Estrechamente Acoplada (TCM) para código de misión crítica.

Desglose Completo de Especificaciones

| Parámetro | Límite Crítico / Nota Técnica |

|---|---|

| Voltaje de Operación | Rango típico de VDD del núcleo; mantener márgenes estrictos para la estabilidad a alta velocidad. |

| Frecuencia Máxima | Máximo nominal del dispositivo; relojes más altos requieren mayores estados de espera de Flash. |

| Estados de Espera de Flash | Escala dinámicamente con SYSCLK; optimice la ubicación del código para mitigar la latencia. |

| Integración de Periféricos | UART/SPI/I2C de alta densidad, muestreo rápido de ADC y canales DMA dedicados. |

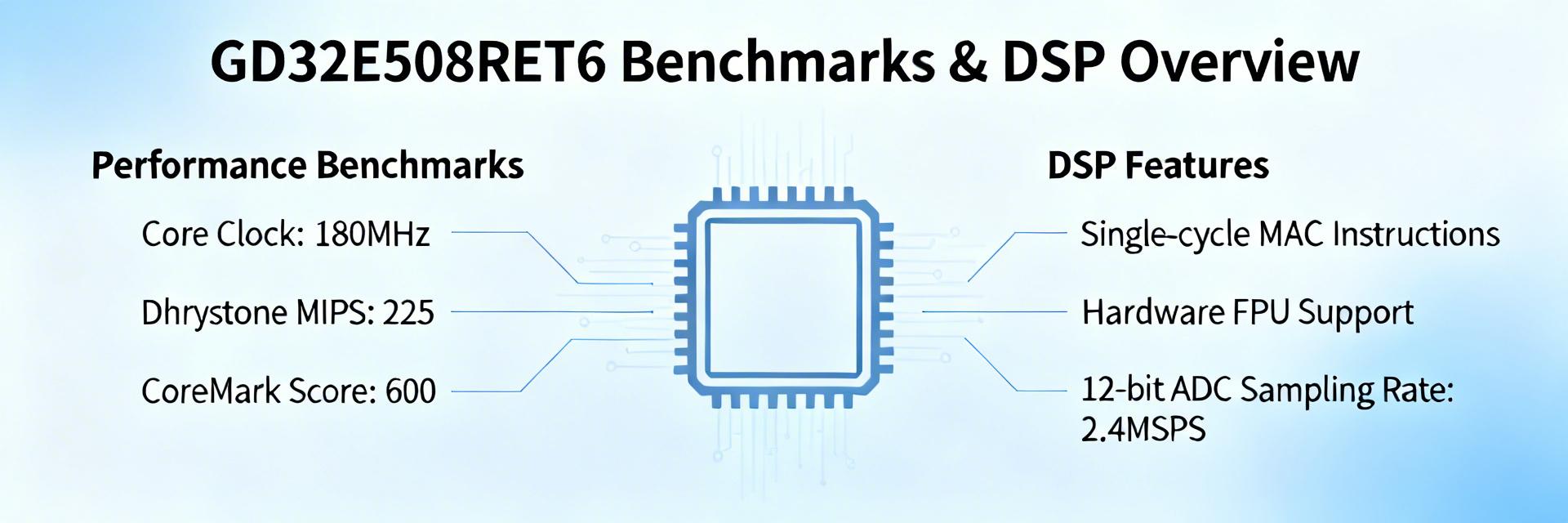

Pruebas de Rendimiento en el Mundo Real

Métricas de rendimiento normalizadas a la frecuencia de reloj máxima utilizando banderas de compilador optimizadas (-O3, LTO).

Integración y Optimización del Rendimiento

Mejores Prácticas de la Cadena de Herramientas

- • Utilice -O3 y LTO para obtener ganancias significativas de rendimiento.

- • Reubique el "código caliente" en TCM para eliminar la latencia de Flash.

- • Aproveche los intrínsecos de hardware CMSIS-NN y FPU para tareas matemáticas pesadas.

Ajuste de Potencia

- • Implemente una desconexión de reloj (clock gating) agresiva para periféricos inactivos.

- • Use el procesamiento por lotes impulsado por DMA para extender la duración del sueño de la CPU.

- • Verifique la latencia de activación frente a los requisitos de la aplicación en tiempo real.

Resumen Ejecutivo

✔ El GD32E508RET6 ofrece un sólido rendimiento DSP de clase Cortex-M33; priorice la ubicación de la memoria para evitar cuellos de botella por estados de espera.

✔ Cumpla con los rangos de voltaje y PLL recomendados para garantizar la confiabilidad a largo plazo y un comportamiento del reloj predecible.

✔ Los resultados de las pruebas (CoreMark, FFT, AES) deben normalizarse por MHz para comparar objetivamente la eficiencia entre diferentes plataformas de silicio.