Este informe técnico examina las tendencias recientes en las pruebas de referencia para microcontroladores de clase Cortex-M4 y explica por qué el GD32E103RBT6 merece una evaluación detallada. Las tendencias observadas enfatizan un rendimiento de enteros competitivo, combinaciones equilibradas de memoria y periféricos, y perfiles de potencia activos/en reposo favorables para tareas embebidas de gama media.

El alcance del informe cubre las especificaciones técnicas clave, la metodología y los resultados de las pruebas de referencia, casos de uso comparativos y recomendaciones de ingeniería accionables diseñadas para una validación rápida y un despliegue confiable.

Estructurado para equipos de ingeniería, el informe proporciona listas de verificación de pruebas reproducibles, plantillas de comparación normalizadas y listas de verificación pragmáticas de hardware y firmware que aceleran el tiempo de prueba de concepto. Está dirigido a diseñadores que evalúan MCUs de gama media para bucles de control, fusión de sensores, control de motores y nodos de telemetría alimentados por batería, ofreciendo umbrales de pasa/falla medibles y tácticas de optimización alineadas con las prácticas de ingeniería globales.

Antecedentes: Posición de Cortex-M4 y Aplicaciones de Destino

Dónde encaja este MCU en el diseño embebido

Punto: La familia Cortex-M4 logra un equilibrio entre el control determinista y las tareas de procesamiento de señales. Evidencia: Los núcleos M4 suelen incluir extensiones DSP y FPU de precisión simple opcional, lo que permite cálculos matemáticos eficientes de enteros y punto flotante para bucles de control y filtrado. Explicación: Para el control de motores en tiempo real, la fusión de sensores y las aplicaciones RTOS de complejidad media, el rendimiento de la clase M4 permite tasas de bucle de control más altas y una menor latencia de interrupción que los núcleos de nivel inferior.

Encapsulado, memoria y envolvente de potencia

Punto: Los diseñadores deben confirmar las limitaciones de encapsulado, memoria y suministro de forma temprana. Evidencia: Los recuentos de pines típicos ofrecen de 48 a 100 pines, flash en el rango de 64 a 128 KB y SRAM en la región de 20 a 32 KB. Explicación: Estos límites definen la disponibilidad de periféricos, las opciones de memoria externa y la estrategia térmica/de potencia para una operación sostenida de alta frecuencia.

| Parámetro |

Valor Típico |

Nota de Ingeniería |

| Encapsulado |

LQFP de 64 pines |

Confirmar el recuento de E/S frente a UART/SPI/PWM requeridos |

| Flash |

|

Planificar el gestor de arranque y la partición OTA |

| RAM |

|

Reservar para pilas RTOS y búferes DMA |

| Vcc |

2.6–3.6 V |

Comprobar la referencia del ADC y la tolerancia de GPIO |

| Recuento de E/S |

~48 GPIO utilizables |

Mapear pines de alta velocidad de forma temprana |

GD32E103RBT6: Especificaciones Técnicas Clave (Detalladas)

Estas especificaciones técnicas resumen el núcleo, los relojes, la arquitectura de memoria y las capacidades de los periféricos para informar las expectativas de las pruebas de referencia y las compensaciones del diseño de hardware.

Núcleo, Relojes y Arquitectura de Memoria

Punto: La revisión del núcleo y el reloj afectan directamente el rendimiento de enteros y el determinismo en tiempo real. Evidencia: El dispositivo utiliza un núcleo de clase Cortex-M4 con una frecuencia de CPU máxima nominal de la clase 108–120 MHz. Explicación: Los diseñadores deben ajustar los estados de espera de la memoria flash y los preescaladores de bus; el mapa de memoria incluye flash interna con bytes de arranque y de opción, además de SRAM embebida.

| Elemento de Especificación |

Valor Nominal |

Nota de Ingeniería |

| Núcleo |

Clase Cortex-M4 |

Verificar soporte FPU/DSP para cargas de trabajo matemáticas pesadas |

| Frecuencia máx. de CPU |

~108 MHz |

Equilibrar rendimiento frente a potencia y estados de espera flash |

| Periféricos |

ADC/DAC/Temporizadores |

Validar rangos de entrada y priorización de DMA |

Pruebas de Referencia y Metodología de Prueba de GD32E103RBT6

Conjunto de Pruebas y Condiciones de Referencia

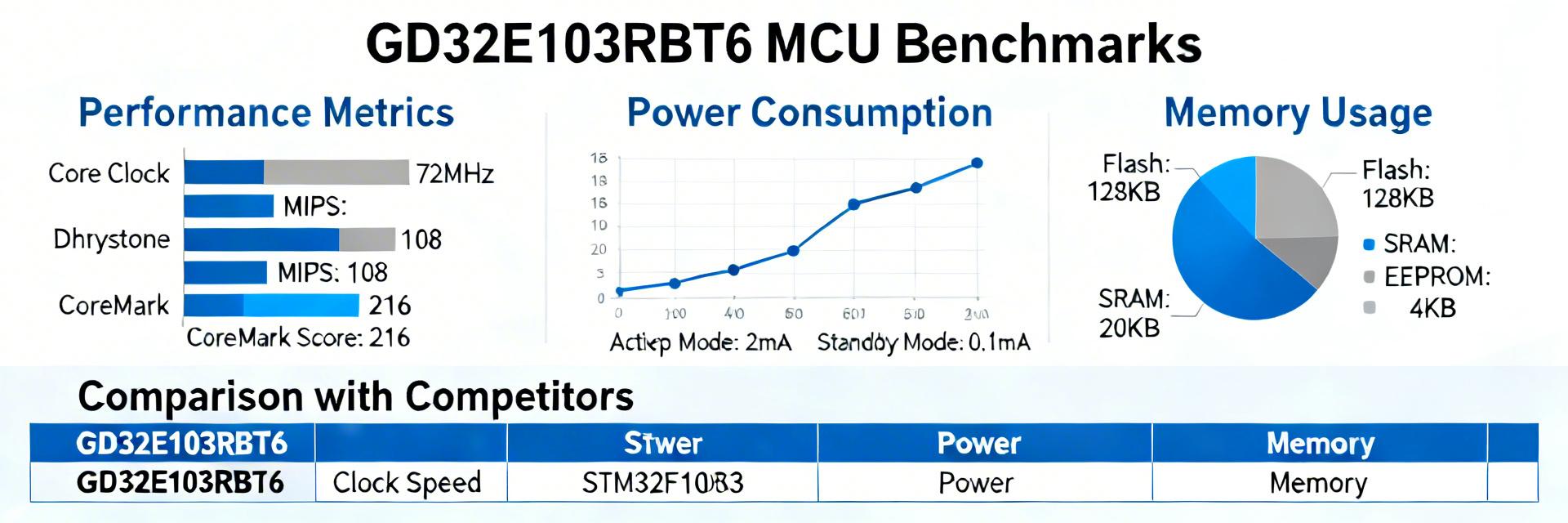

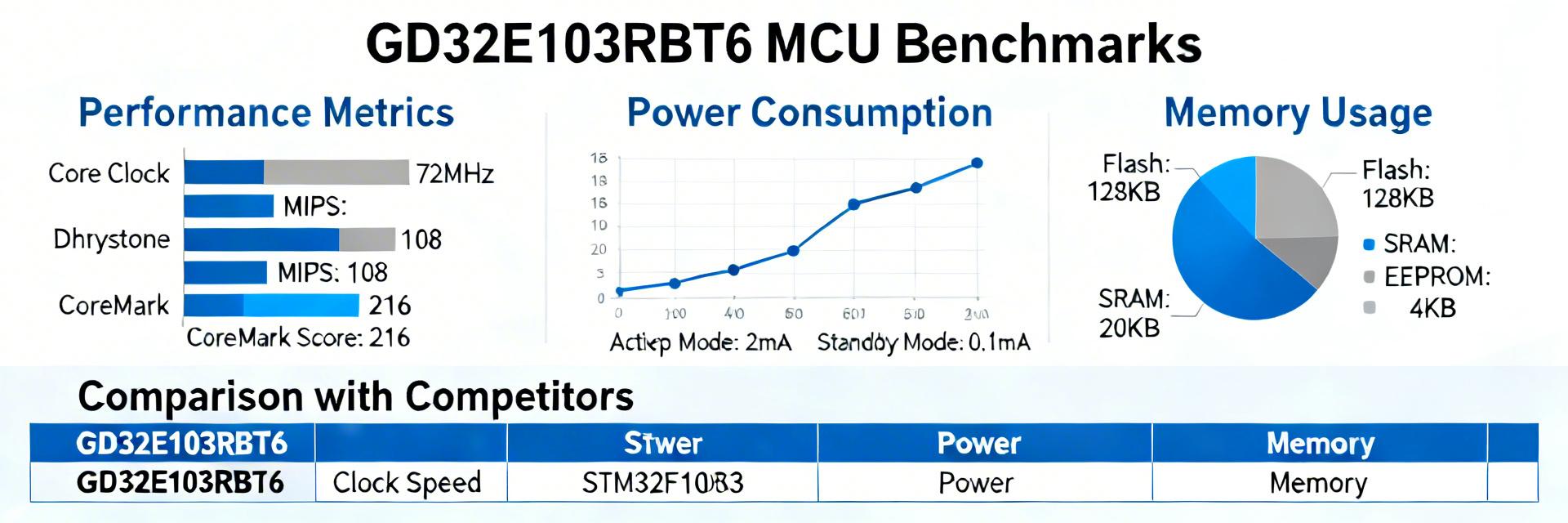

Punto: Las pruebas de referencia reproducibles requieren cadenas de herramientas y condiciones de medición definidas. Evidencia: El conjunto recomendado incluye CoreMark, Dhrystone (DMIPS/MHz), micro-referencias de enteros/punto flotante y rendimiento de memoria. Explicación: Utilice un compilador consistente con indicadores de optimización explícitos (por ejemplo, -O3), configuración de reloj fija y medidores de potencia calibrados.

Métricas Clave y Presentación

Punto: Seleccione métricas que se ajusten directamente a los requisitos del sistema. Evidencia: Informe la puntuación CoreMark, DMIPS/MHz y MB/s de lectura/escritura de memoria. Explicación: Presente los resultados con gráficos de barras para las puntuaciones del núcleo y tablas para la potencia frente a la frecuencia para que los resultados sean procesables.

Lista de Verificación de Diseño de Hardware

-

✔ Desacoplamiento cercano en los pines Vcc

-

✔ Tierra analógica dedicada para entradas ADC

-

✔ Enrutamiento cuidadoso del cristal y filtrado EMI

-

✔ Implementar configuraciones de caída de tensión y reinicio

Lista de Verificación de Ajuste de Firmware

-

⚙ Usar indicadores de compilador específicos de la arquitectura

-

⚙ Alinear código crítico a regiones de memoria más rápidas

-

⚙ Habilitar FPU/DSP por hardware para cargas matemáticas

-

⚙ Emplear el gating de reloj para periféricos no utilizados

Resumen

- El GD32E103RBT6 ofrece una combinación equilibrada de gama media de clase Cortex-M4 con rendimiento de núcleo, periféricos integrados y potencia manejable para aplicaciones de control y detección.

- Adopte la lista de verificación de pruebas y las plantillas de normalización proporcionadas para garantizar comparaciones justas e identificar cuellos de botella en los estados de espera de flash y DMA de forma temprana en el desarrollo.

- Siga las listas de verificación de hardware y firmware (desacoplamiento, front-end de ADC, indicadores de compilador y gating de potencia) para reducir los ciclos de iteración y el riesgo al escalar a la producción.

Preguntas Frecuentes

¿Qué pruebas de referencia de rendimiento debo ejecutar para el GD32E103RBT6?

+

Ejecute CoreMark y Dhrystone para la comparación a nivel de CPU, micro-referencias para los núcleos de enteros/punto flotante utilizados por su firmware, pruebas de rendimiento de memoria para DMA y pruebas de estrés de muestreo de ADC. Incluya mediciones de potencia en cada frecuencia y caso de carga para correlacionar el rendimiento con el consumo de energía.

¿Cómo optimizo la potencia para diseños con batería usando este MCU?

+

Utilice el gating de periféricos y reloj para deshabilitar bloques no utilizados, seleccione el reloj más bajo viable para los estados de inactividad y use DMA para mantener la CPU en modos de bajo consumo. Elija un regulador eficiente (buck para amplios rangos de entrada), configure correctamente la caída de tensión/reinicio y verifique las latencias de sueño/despertar frente a sus ventanas de muestreo.

¿Cuáles son los errores comunes al realizar pruebas de referencia y validar esta clase de MCU?

+

Los errores comunes incluyen indicadores de compilador inconsistentes, estados de espera de flash no informados que limitan el rendimiento en relojes altos, control térmico insuficiente al medir la potencia e ignorar el jitter inducido por ISR. Mitigue estos automatizando las ejecuciones y documentando la configuración de la cadena de herramientas.